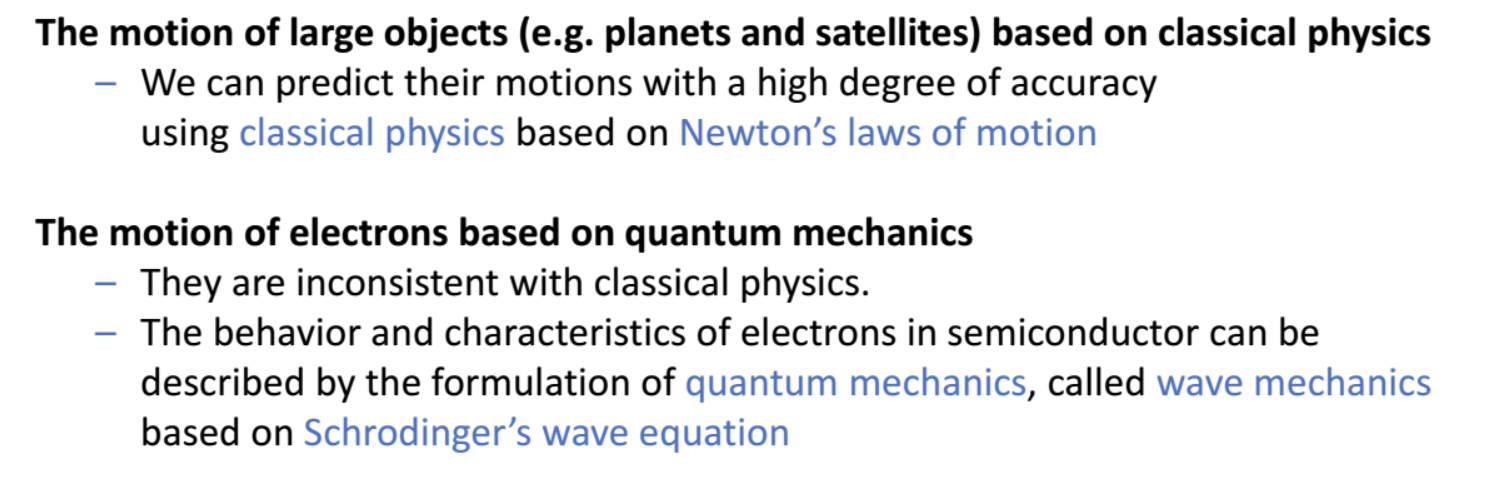

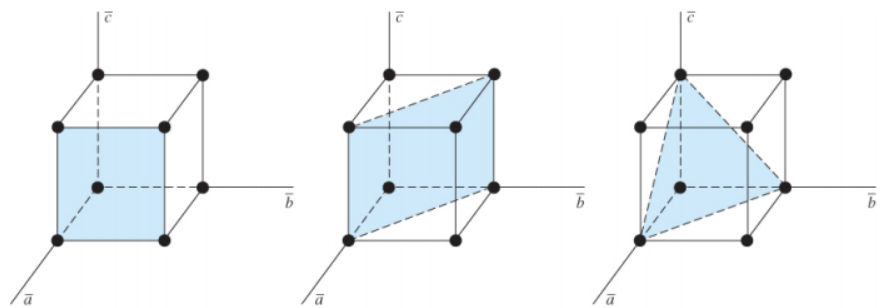

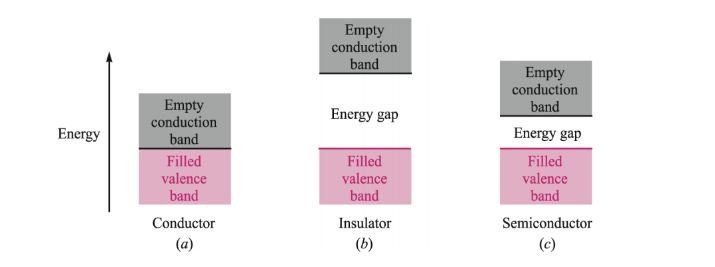

Quantum Mechanics Electron & Hole : 크기가 작고 질량도 작아서 우리가 알고 있는 일반 물리학 적용이 안 된다. (결과가 불확실) 전자와 정공에 대해서는 Quantum(양자) Mechanics(역학) 도입이 필요하다. //확률적 접근 ** 양자 : 에너지가 연속적이지 않고, 뚝뚝 끊어져있다. or 수치화 되어있다. 연속적이지 않은! (이산화 된 에너지) ** 역학 : 물체의 운동 거시적인 움직임 vs cubic 안에 전자가 있을 확률 Semiconductor Energy gap (C) Semiconductor : 외부의 에너지(빛. 열, 전압 etc..)에 의해서 전류가 흐를 수 있게 만들 수 있는 것으로, 외부 에너지에 의해 valence band에 있는 전자가 conduct..