Dataflow Modeling

RTL system

*** RTL(Register Transfer Level) system is a combination of dataflow and behavioral modeling.

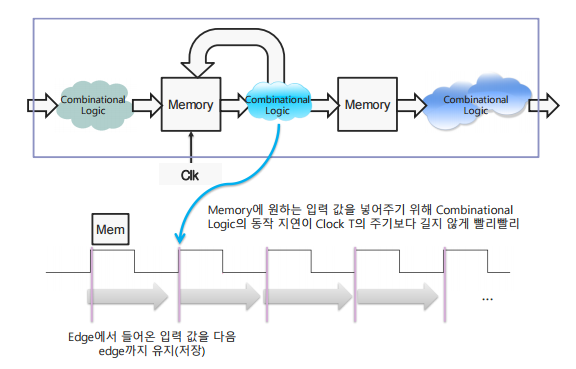

: Any digital system can be constructed by interconnecting registers(Flip Flop) and a combinational logic put between them for performing the necessary functions.

// 모든 디지털 시스템은 상호 연결된 register(FF)로 연결되어있고 register사이에는 combinational logic이 있다.

Register 사이에 있는 Combinationla Logic의 동작 지연은 clock 주기인 T보다 길지 않아야 한다.

Clk Edge전에 Comgination logic 동작을 완료하여 값을 준비해놓아야 delay가 생기지 않는다.

Why dataflow? ( Rationale of dataflow )

- Dataflow provides a powerful way to implement a design.

- Provides Circuit Descrtiption in terms of Data flow between register and processes on Data rather then gate instantiation

//gate가 아닌 register와 processes(combinational logic)

- Is expressed by continuous Assignments and operators

//c에서의 assignment(=)처럼 오른쪽에 있는 거 계산해서 왼쪽에 전달하

- Logic synthesis tools can be used to create a gate-level circuit from a dataflow design description.

- RTL level로 설계 ( FF들이 있고 그 사이를 dataflow로 넣는 )

Continuous Assignments

: The most basic statement of dataflow modeling.

- It is used to drive a value onto a net.

- It is always active

// 언제든지 미리 정의된 값 또는 표현식을 할당할 수 있는 상태임을 의미한다.

따라서, 값이 변할 때마다 해당 연산이 실행될 수 있고, 언제든지 연속적으로 값이 할당될 수 있음을 의미한다.

- Any logic function can be realized with continuous assignments.

- It can only update values of net data types such as wire, triand, etc.

left part는 wire이다. 왼쪽은 flip flop이 아닌 wire에 실어줘야 한다.

- Dataflow는 FF에 저장하기 전에 Combinational logic 만드는 단계이다.

따라서 아직 저장하는 건 다루지 않고, left part는 무조건 wire 혹은 FF에서 가져온 값이다. ( net에 drive하는 개념)

[Explicit] //가장 추천하는 방식

wire out; // regular continuous assignment

assign out = in1 & in2;out에 in1과 in2를 and시켜서 넣었는데, 여기서 assign key-word를 명시적으로 붙여주었다. //C와의 차이점!

[Implicit] //비추천

wire out = in1 & in2; // implicit continuous assignmentassign을 따로 쓰지 않고, wire를 생성함과 동시에 assign 시킬 수도 있다.

[too....implicit]

wire in1, in2;

assign out = in1 & in2;out이 wire로 선언되지 않았다. 하지만, assign으로 out에 값을 할당해줌으로써, simulator에 의해 out에 대한 선언이 암묵적으로 이루어진다.

하지만, 이는 wire가 1bit로 동작이 가능했기 때문에 정상적으로 작동했으며, wire가 1bit이상일 때는 오류가 생긴다.

//1bit wire는 생략할 수 있다!.....그치만 생략은 오류를 생성할 확률을 높이니.... 명시적으로 assign하기!~