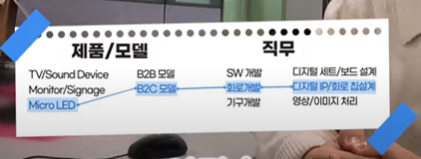

영상디스플레이 사업부 회로개발 youtube.com/watch?v=WdZosdW8k9U&list=PLTHa7qutpLjCrQEHA5KXDnT7MwKlb2jcK&index=12 VD 사업부 (영상 디스플레이 사업부) : 다양한 환경에 맞는 최적의 display 제품을 개발해 소비자에게 최고의 솔루션을 제공하고 소비자 개개인의 라이프스타일을 반영한 제품을 개발하는 부서 이광호 프로 : VD사업부의 혁신제품개발 Lab 제품선행 FPGA 파트 근무 제품마다 있는 analog 회로 위에 Firmware를 얹어서 실제 전기적 신호를 컨트롤 하고 불이 들어오게끔 연구(TV나오도록) 혁신 제품 개발 Lab : LED 기반의 디지털 사이니지와 Micro LED 디스플레이 "The wall" 제품의 TCON,FPGA(fi..