LFSR

LFSR이란?

: Linear Feedback Shift Register의 약자로, 선형 되먹임 시프트 레지스터이다.

Shift Register에 입력되는 값이 이전 상태의 선형 함수로 다시 되먹임되는 Linear Feedback구조이다.

이전 상태가 Feedback되어 다음 상태를 만들기 때문에 "결정론적이다"라고 할 수도 있다.

Fibonacci LFSR

module fibonacci_LFSR(

input clk,

input arst_n,

output LFSR

);

parameter BITWIDTH = 5;

//bitwidth만큼 reg생성

output reg [BITWIDTH -1 : 0 ] LFSR;

always @(posedge clk or negedge arst_n) begin

if(!arst_n) begin

LFSR <= 1; //00001

end

else begin

//0,4번째BIT xor하여 msb로 feedback, 나머지는 shift to right

LFSR <= {LFSR[0]^ LFSR[4], LFSR[ BITWIDTH-1 : 0 ]}

end

end

endmodule

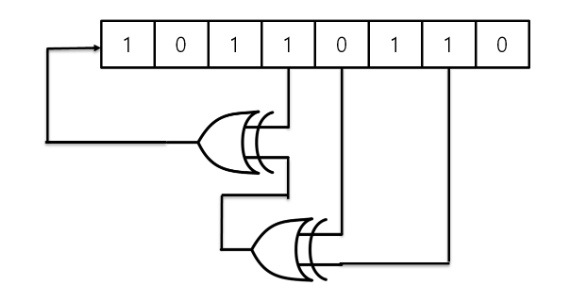

Galois LFSR

Galois LFSR

: Galois LFSR은 주로 난수 생성기, 순차 회로, 암호화 등의 분야에 사용된다.

LFSR은 일련의 binary 값들을 저장하는 장치이다. Feedback loop는 xor gate를 사용하여 구현된다.

LFSR은 SEED상태에서 시작하여 주기를 가지며, 주기가 반복될 때마다 난수 시퀀스를 생성한다.

모든 BIT가 0일 때에는 주기를 가지는 것이 불가능하다. (SEED값을 0으로 하지 않아야함)

따라서 적절한 초기 상태를 선택함으로써 LFSR은 무작위 수열을 만들 수 있다.

Galois LFSR은 특정 조건에서 예측 가능성이 있으므로 암호화용으로는 취약하나 단순 난수 생성으로는 사용된다.

- LSB와 Tap + 1번 bit를 XOR시커 Tap에 feedback한다.

- XOR 게이트를 하나씩만 가지므로 fibonacci보다 critical path가 짧다.

module galois_LFSR(

input clk,

input, arst_n,

output LFSR

);

paramter BITWIDTH = 5;

output reg [BITWIDTH-1:0] LFSR;

always @(posedge clk or negedge arst_n) begin

if(!arst_n) LFSR <= 1;

else LFSR <= {LSFSR[0]^1'b0, LFSR[4], LFSR[3]^LFSR[0], LFSR[2], LFSR[1]};

end

위 코드는 TAP이 3인 코드이다. 따라서 TAP+1인 4번 BIT를 1번과 XOR시켜 3번에 FEEDBACK해준다.

'Quality control (1) > Verilog' 카테고리의 다른 글

| Verilog 결과값 저장 / fopen / fwrite (0) | 2024.01.25 |

|---|---|

| Verilog - Finite State Machine (FSM) / Lemming Game (0) | 2023.05.17 |

| Verilog - 4bit Ripple Carry Adder (0) | 2023.03.21 |

| Verilog - Synthesis (full_adder_dataflow) / LUT / truth table (2) | 2023.03.20 |

| Verilog - mux4_to_1 & test bench (0) | 2023.03.16 |