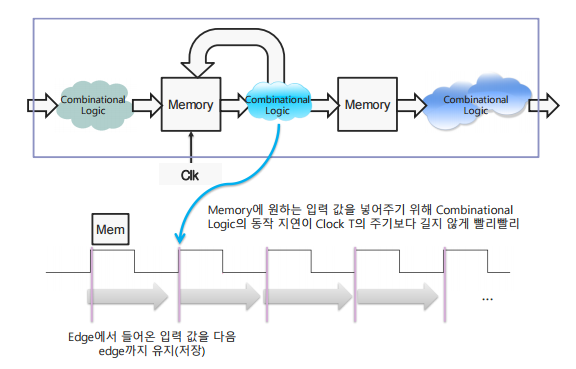

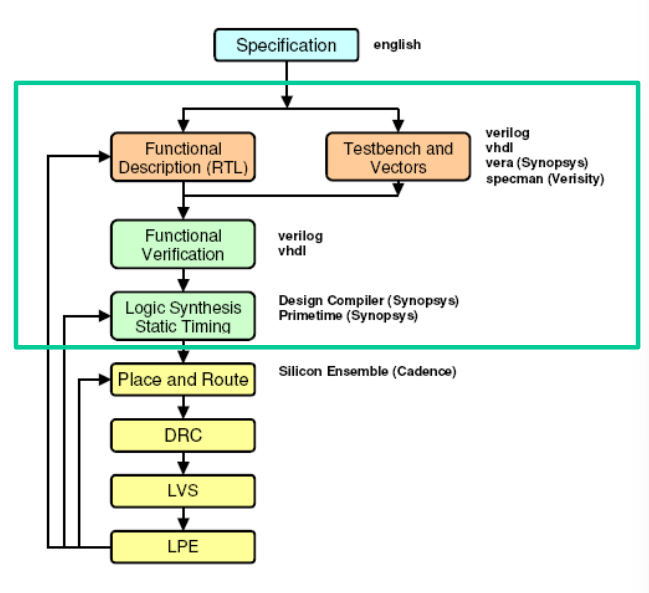

Behavioral Modeling Behavioral Modeling - This level describes a system by concurrent(동시) algorithms. - 각각의 알고리즘들은 순차적이다. //전체적으로는 concurrent하나, algorithm내에서는 sequential 순차적이라는 것은 하나씩 실행되는 명령어들의 집합으로 이루어졌다는 것을 의미한다. - Functions, Tasks , always blcok이 main element이다 ( 6주차에 배움) - no regard to the structural realization of the design [GPT said] Behavioral modeling is a type of high-level abstractio..