Synthesis

full_adder_dataflow

module full_adder_dataflow(

x,y,c_in,

sum,c_out

);

input x,y,c_in;

output sum,c_out;

assign {c_out,sum}=x+y+c_in;

endmodule

위 코드를 작성하고 schematic을 확인하면 위와 같이 RLD_ADD를 확인할 수 있으나, RTL_ADD가 실제로 어떤 gate들로 이루어지는지 알 수 없다. 이 때 Verilog code의 gate합성을 확인할 수 있는 도구가 바로 sythesis이다.

Synthesis

: High-level language 를 Low-level language로 변환하는 것을 일반적으로 Synthesis라고 한다.

디지털 시스템 설계에서의 Synthesis는 verilog / VHDL 코드를 gate-level netlist로 변환하는 과정을 말한다.

(Vivado synthesis 유의사항)

- synthesis하려는 module이 top module로 설정되었는지 확인하고 top이 아닐경우에 as a top 클릭한다.

- number of jobs는 사용할 core수를 결정하는 것이다. 최대개수 혹은 최대개수보다 하나 적은 것을 선택한다.

synthesis를 통해 gate level로 변경해준 뒤에 schematic을 통해 module이 다음과 같이 합성된 것을 확인할 수 있다.

- IBUF / OBUF

: analog 회로 레벨에서 Delay개선을 위해 필요한 buffer로, 자동으로 생성된다.

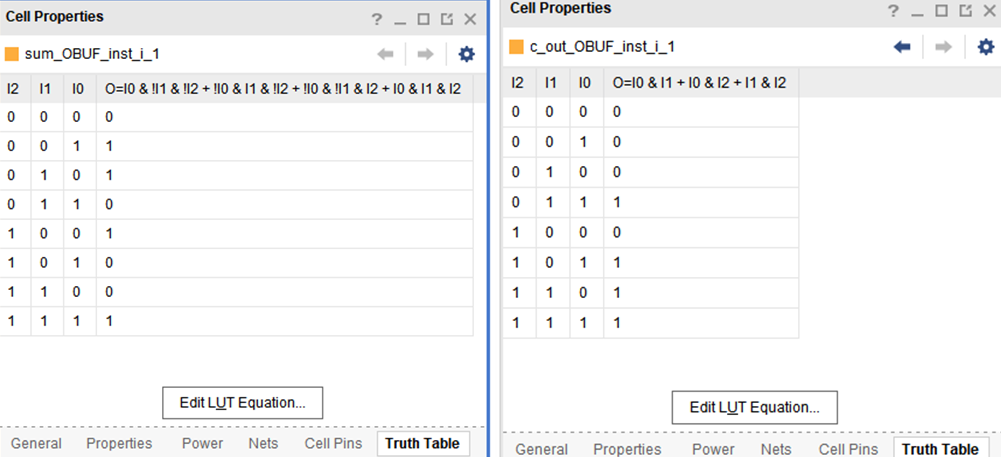

LUT ( Look Up Table )

: ( FPGA의 장점으로, gate level로 합성하는 것보다 LUT에서 값을 읽는 것이 더 빠르고 POWER소모가 적다. )

LUT stands for "Look-Up Table", which is a type of data structure used in computer science and digtal signal processing. A Look-Up Table is essentially a pre-calculated table that maps input vales to output vales based on a given function or algorithm.

Truth table 확인 방인 방법

: schematic에서 LUT 부분을 클릭하고 좌측 Cell Properties -> Truth Table 클릭!

'Quality control (1) > Verilog' 카테고리의 다른 글

| Verilog - Finite State Machine (FSM) / Lemming Game (0) | 2023.05.17 |

|---|---|

| Verilog - 4bit Ripple Carry Adder (0) | 2023.03.21 |

| Verilog - mux4_to_1 & test bench (0) | 2023.03.16 |

| Verilog - 8case_4true / boolean expression / schematic (0) | 2023.03.16 |

| Verilog Basics - Module modeling / Test bench 실습 (0) | 2023.03.15 |