Verilog Basic - hw(1)

과제(1)

- 3bit binary(A,B,C)로 표현된 7가지 경우에 대하여 m0,m2,m6,m7에 대해서만 true(y=1)

Boolean Expression

Y = A'C' + AB

wire 구현

: wire는 초반에 선언을 모두 하지 않고, main body에서 gate들을 구현하며 필요로 하는 것을 추가하여 선언한다.

Verilog Design source

module _8case_4true(out, i0, i1, i2);

//output,input declaration

output out;

input i0,i1,i2;

//wire declaration

wire n0,n2;

wire a0,a1;

//gate declaration

//not gate

not (n0,i0);

not (n2, i2);

//and gate

and (a0, n0, n2);

and (a1, i0, i1);

//or gate

or (out, a0, a1);

endmodule

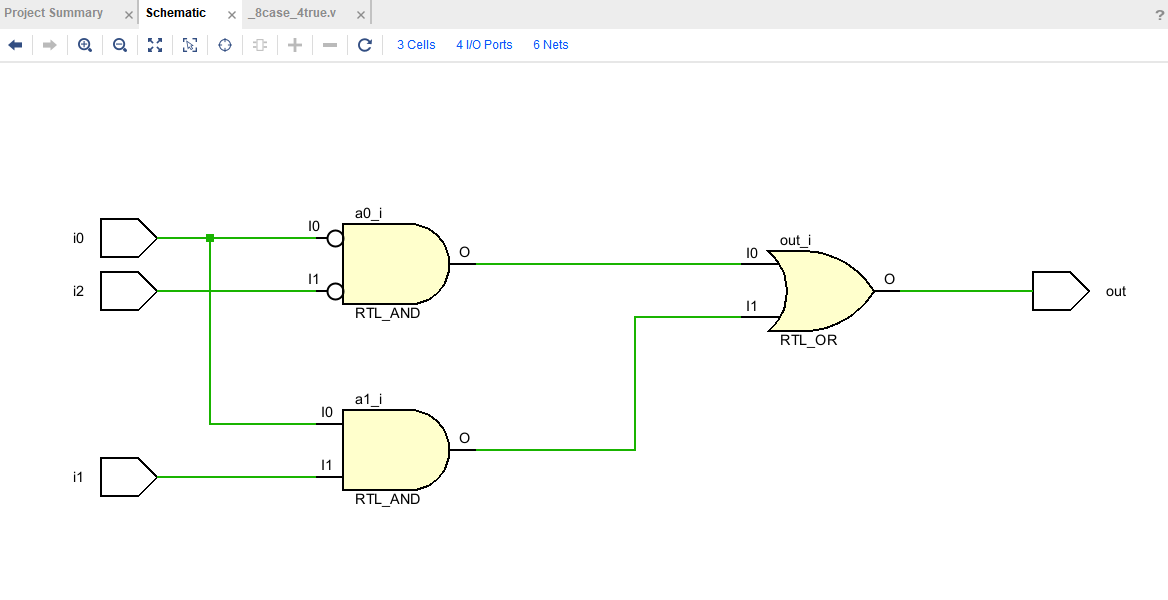

schematic

synthesis report

???

test bench code

module tb_8case_4true();

//Stimulus Declaration (input)

reg IN0, IN1, IN2;

//Response Declaration (output)

wire OUTPUT;

//object

_8case_4true mycase (OUTPUT, IN0, IN1, IN2);

//stimulus

initial begin

IN0 = 0; IN1 = 0; IN2 = 0;

#5 IN0 = 0; IN1 = 0; IN2 = 1;

#5 IN0 = 0; IN1 = 1; IN2 = 0;

#5 IN0 = 0; IN1 = 1; IN2 = 1;

#5 IN0 = 1; IN1 = 0; IN2 = 0;

#5 IN0 = 1; IN1 = 0; IN2 = 1;

#5 IN0 = 1; IN1 = 1; IN2 = 0;

#5 IN0 = 1; IN1 = 1; IN2 = 1;

end

endmodule

simulation result

'Quality control (1) > Verilog' 카테고리의 다른 글

| Verilog - Finite State Machine (FSM) / Lemming Game (0) | 2023.05.17 |

|---|---|

| Verilog - 4bit Ripple Carry Adder (0) | 2023.03.21 |

| Verilog - Synthesis (full_adder_dataflow) / LUT / truth table (2) | 2023.03.20 |

| Verilog - mux4_to_1 & test bench (0) | 2023.03.16 |

| Verilog Basics - Module modeling / Test bench 실습 (0) | 2023.03.15 |