- Flip flop 의 state는 clk만 바꿀 수 있다. FF과 clk은 절친~!

- latch의 always sensitive list에 en(or clk)이랑 D 모두 넣어야함 (en=1인동안 D가 바뀌면 바로 반영해야 하니까)

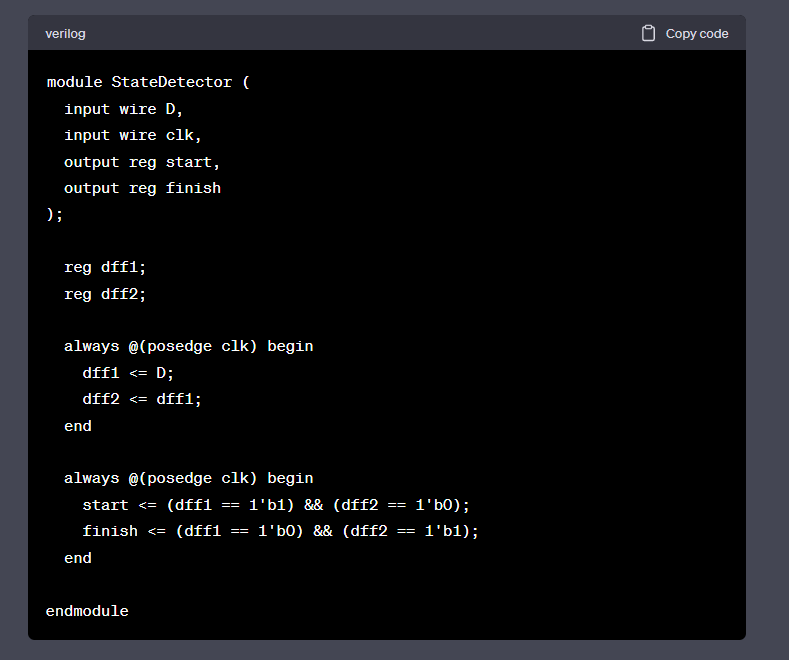

- state 시작과 끝 알아내기

- SRAM : static random access memroy (register file만들 때 사)

- DRAM : dynamic random access memory

- 6-transistor COMS SRAM cell (BL:bit line, WL:word line)

- main disk가 있지만, 거기서 다 가져오면 시간이 오래 걸리므로, 여러개의 작은 것들 배치

register < cache(SRAM,register file) < Memory (DRAM) < disk

오른쪽으로 갈 수록 저장공간은 작아지지만 가져오는 속도는 빨라짐

- CPU = ALU( arithemetic logic unit ) + register

//register는 보통 arithemetic을 위한 operrand를 가져오는 용도로 사용

- sram에서는 read,write 동작을 하나의 alwyas문 안에서 sequential로 수행해야해 (wr 제어로)

기존 register file처럼 read는 combinatianal lobic으로 바로바로 빼올 수 없어

- Binary ripple counter에서 다음 flip flop의 clk이 되는 요소들 assign 변수로 따로 빼두기

ex) assing c2=qout[2], c1=qout[1];

-Flip Flop 값의 반전을 사용할 때, 반드시 reset을 통해 초기화를 해주고 시작해야한다.

garbage값에 대한 반전으로 시작해버리면 코드 수행 x

- Binary ripple counter에서 flip flop을 reset하는 것도 각자의 always문 안에서 따로따로 진행

'Quality control (2) > Digital System Design' 카테고리의 다른 글

| DSD - Digital system Field words (1) | 2023.06.04 |

|---|---|

| DSD - Logic Synthesis (0) | 2023.06.02 |

| DSD - ASIC Design Flow (0) | 2023.06.02 |

| DSD - Behavioral Modeling(2) / Procedure constructs (always) (0) | 2023.04.06 |

| DSD - Behavioral Modeling(1) / Procedure constructs ( initial ) (0) | 2023.04.06 |