SPICE (inverter)

SPICE 파일 (.sp) 만들기

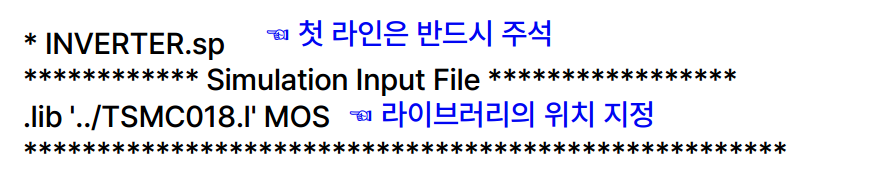

[Simulation input file]

- 첫 라인은 반드시 주석으로 작성한다.

- 라이브러리의 위치 지정 필요

[Condition]

- option scale : spice simulation에서 사용할 길이 단위

- global VDD GND : 전역 노드로 'VDD'와 'GND'를 정의한다. 회로에서 전원 공급 및 전압을 나타내는 노드로 사용

- temp : 시뮬레이션을 위한 온도를 설정한다. 섭씨 기준으로 작성된다.

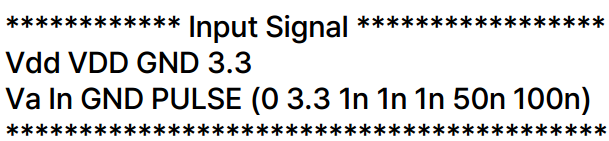

[Input Signal]

-input signal 입력 순서

: 입력신호이름 -> IN -> OUT -> IN과 OUT 사이 전압

Vdd VDD GND 3.3 //Vdd라는 input 전원 source 생성, VDD와 GND 사이 전압은 3.3v

Va In GND PULSE (0 3.3 1n 1n 1n 50n 100n) // In과 GND 사이 PULSE- VDD: 전압노드 , GND : 접지노드

- In : 신호가 적용될 노드 , GND : 동일 노드

- PULSE ( 0 3.3 1n 1n 1n 1n 50n 100n )

0: 파형 시작 시간 (t1), 이 경우 0초부터 시작합니다.

3.3: 파형 최대 값 (A), 이 경우 3.3V로 설정됩니다.

1n: 상승 시간 (tr), 이 경우 1나노초로 설정됩니다.4

1n: 유지 시간 (pw), 이 경우 1나노초로 설정됩니다. 이 시간 동안 파형이 최대 값으로 유지됩니다.

1n: 하강 시간 (tf), 이 경우 1나노초로 설정됩니다.

50n: 주기 (per), 이 경우 50나노초로 설정됩니다. 이 주기마다 파형이 반복됩니다.

100n: 반복 횟수 (td), 이 경우 100나노초 동안 파형이 생성됩니다.

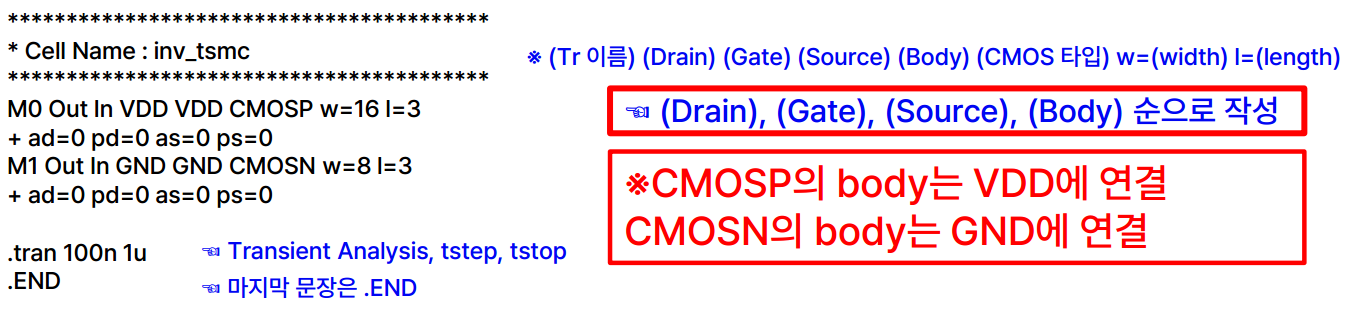

- * Cell Name

: inv_tsmc: 주석으로 "inv_tsmc"라는 셀 이름을 나타냅니다. 이 셀은 CMOS 인버터를 나타내는 것으로 보입니다.

- Transient analysis

: 시간 도메인 시뮬레이션으로, 전자회로에서 시간에 따른 신호의 변화를 시뮬레이션하고 분석하는 과정들을 의미한다.

- 코드 분석

[PMOS]

M0 Out In VDD VDD CMOSP w=16 l=3

+ ad=0 pd=0 as=0 ps=0

[NMOS]

M1 Out In GND GND CMOSN w=8 l=3

+ ad=0 pd=0 as=0 ps=0

M0 : transistor 의 이름 (또는 인덱스)

Out : 출력 노드 이름 (Drain)

In : 입력 노드 이름 (Gate)

VDD VDD : drain과 source가 연결되는 전원 공급 노드

CMOSP : 해당 transistor가 P-MOS 트랜지스터임을 의미

w=16 : transistor의 width가 16

l=3 : transistor의 lenght가 3

ad=0 pd=0 as=0 ps=0 : 다양한 기술적인 특성을 설정하는 추가 파라미터

.tran 100n 1u

.END

시간 도메인 (transient analysis) 시뮬레이션을 설정한다.

100ns는 종료 시간을 의미하고 1u는 시뮬레이션 스텝 크기를 의미한다.

.END는 SPICE 코드의 끝을 나타내며, 이 줄 이후에는 더이상 코드가 없음을 의미한다.

'Quality control (2) > Digital Integrated Circuit Design' 카테고리의 다른 글

| DIC - 축약어 정리 (0) | 2023.10.04 |

|---|